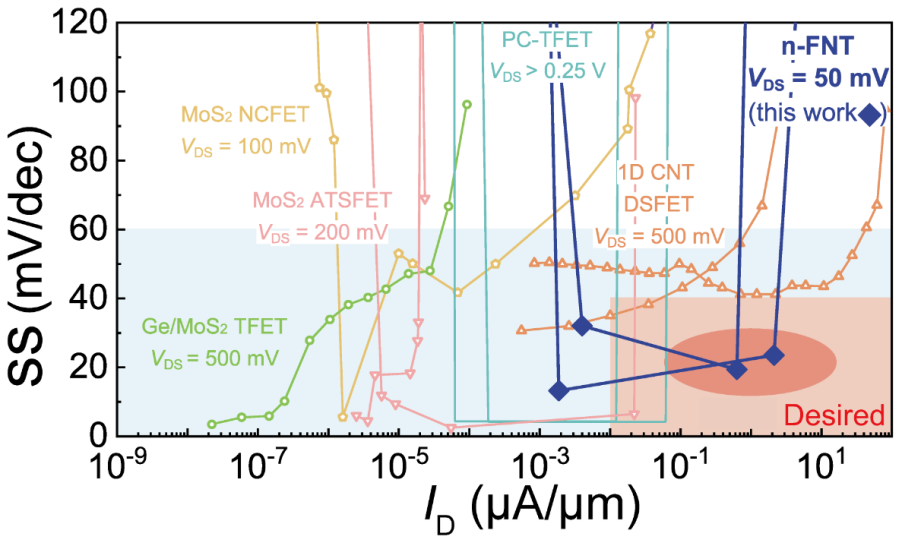

当今,传统硅基晶体管的关键尺寸逐渐逼近物理极限,器件性能的提升面临诸多挑战,如短沟道效应等。在超摩尔定律的新时代,降低芯片功耗成为集成电路发展的主要趋势。主要挑战之一是降低工作电压以实现动态功耗的降低。在传统CMOS技术中,尽管晶体管关键尺寸的微缩一直在进行,但工作电压近年来没有显著降低。这是由于亚阈值摆幅(SS)被限制在不低于60 mV dec−1(室温下)。因此,学术界和业界都在积极开发新材料和新原理来克服这一限制。目前,研究者已经提出多种陡坡器件原型(SS < 60 mV dec−1),如隧道场效应晶体管、狄拉克源场效应晶体管、负电容场效应晶体管,纳机电场效应管和相变场效应晶体管等。然而,开发具有高陡坡电流密度的晶体管仍是目前的一大挑战。

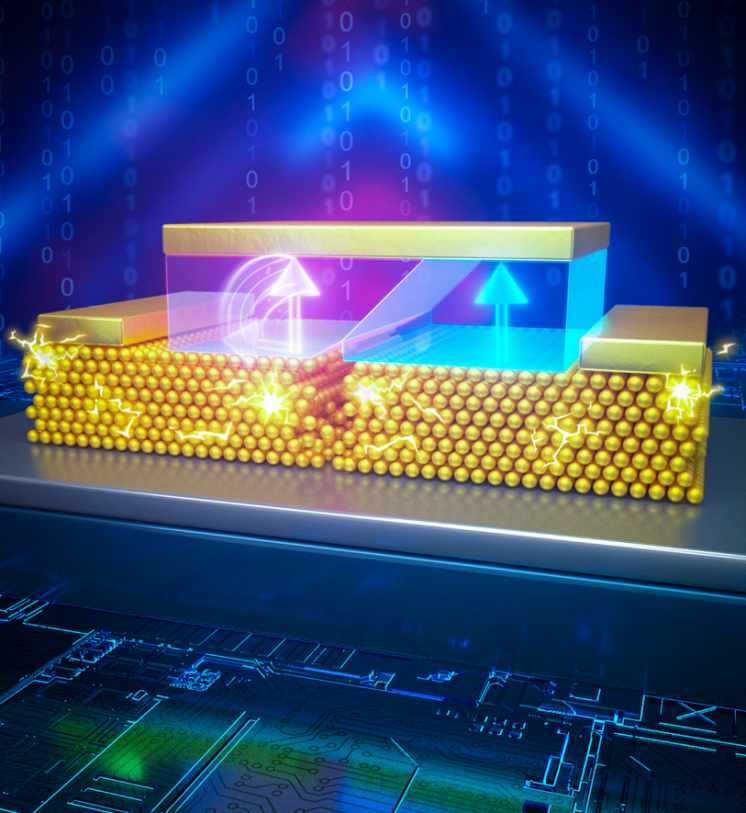

近日,我院博士生关曜东和博后郭喆在新型陡坡晶体管领域取得新进展,利用电学切换的纳隙去构筑陡坡晶体管。此纳隙晶体管可以在高电流密度且跨越5个数量级的范围内获得15.9 mV dec−1的平均SS值。另外,该晶体管还具有接近零的泄漏电流、高导通电流以及双极型翻转等特点。相关成果以题为“Ferroelectric Nanogap-Based Steep-Slope Ambipolar Transistor”发表在期刊《Small》上,华中科技大学为论文第一和通讯单位,游龙教授为论文通讯作者,博士生关曜东和博士后郭喆为论文共同第一作者。

在电场作用下,铁电单晶中的铁电畴会发生特定翻转。游龙课题组在之前的研究工作中发现,翻转产生的弹性能可以沿畴边界诱导出纳隙。如果铁电体顶部有一层金属薄膜,也会在薄膜中产生纳隙。因此,可以使用简单的方法来制备极小的空气纳隙,而不像传统的纳机电开关那样涉及复杂的制造工艺。

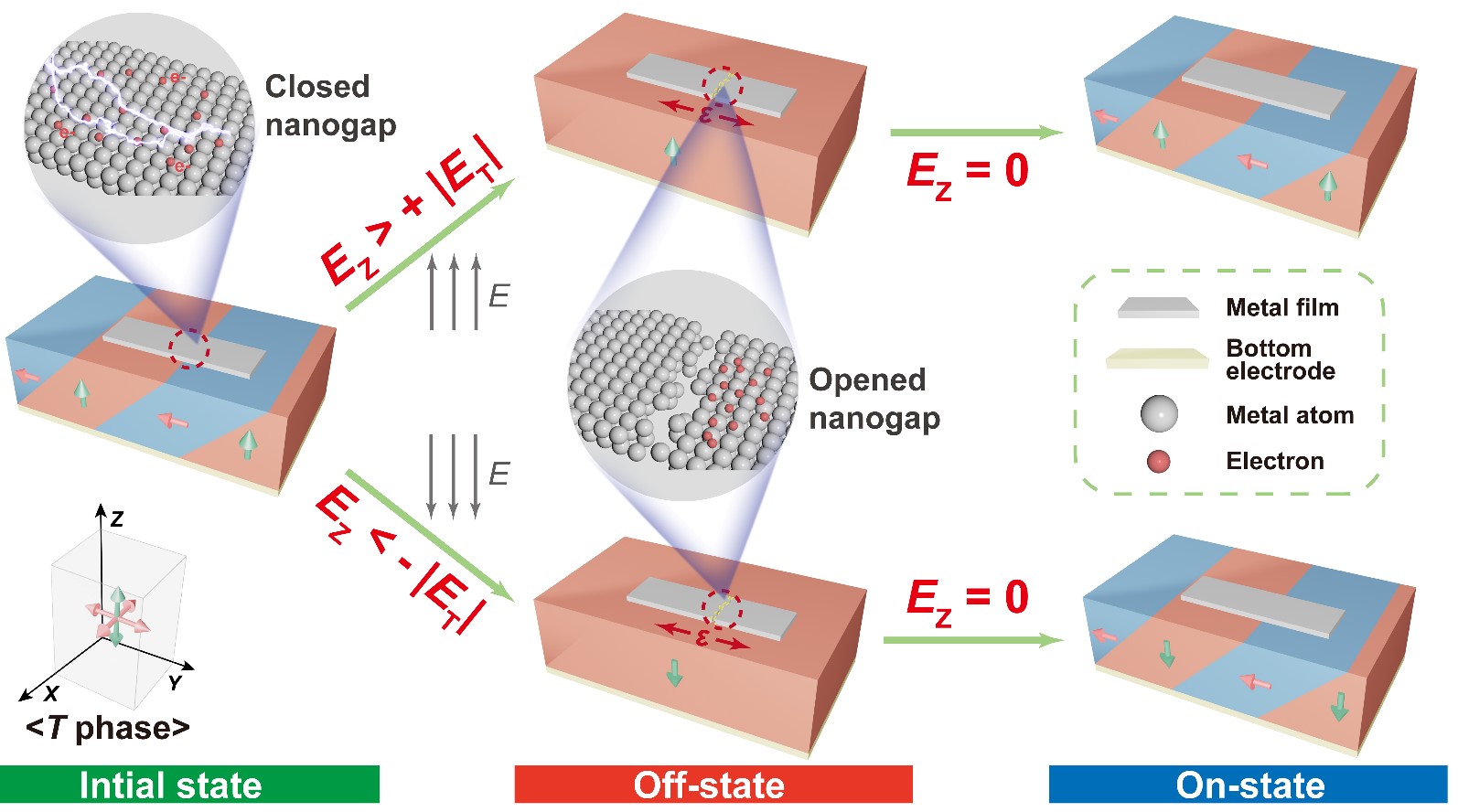

纳隙晶体管的原型结构由四方相BaTiO3铁电单晶与其上方的MnPt/Pt金属膜层构成。四方相的铁电氧化物通常有六种自发极化方向,可以分为面外(c畴)和面内(a畴)两种畴。随着垂直电场EZ正向增加至阈值电场ET,a畴翻转为c畴。相应地,在畴边界产生面内拉伸应变(ε),金属膜层中的纳隙被随之打开。此时,晶体管源漏电极之间被空气隔开,没有电流流动,对应晶体管的关断状态。EZ的继续增加使得局部区域保持单畴状态(或不稳定状态)。相反,当EZ重新降低至阈值附近时,从能量最优角度出发,此区域会再次形成多畴状态,铁电畴可能会恢复到与先前相同的结构。此时,纳隙闭合,源漏电极之间恢复欧姆接触,对应晶体管的闭合状态,且具有小的回滞。类似地,随着EZ的负向增加,所有的畴都翻转到-z方向,再次引起面内拉伸应变,导致晶体管再次关断。因此,该纳隙晶体管具有双极开关特性。

该工作对纳隙晶体管通过类机械切换方式来摆脱亚阈值摆幅限制进行了概念验证,其获得了15.9 mV dec−1的平均SS值和13.23 mV dec−1的最小SS值。重要的是,该晶体管具有小的SS值的同时保持了高的导通电流密度,这对于晶体管在逻辑计算方面具有重要意义。纳隙晶体管有望成为后摩尔时代新的候选方案,为新兴晶体管器件和铁电畴工程的高效运用提供了设计指导原则。

该成果得到了国家自然科学基金、国家重点研发计划、武汉强磁场中心跨学科规划和中国博士后基金等项目的支持。