近日,我院大四本科生吴加隽同学在集成电路工程系王超研究员的指导下,其研究工作被国际电路与系统领域顶级期刊IEEE Transactions on Circuits and Systems I: Regular Papers(TCAS-I)接收,论文题目为“Efficient Design of Spiking Neural Network with STDP Learning Based on Fast CORDIC”[1]。该论文提出了一种基于快速收敛CORDIC算法(Fast-convergence CORDIC)的类脑脉冲神经网络(SNN)高能效处理器硬件实现。论文第一作者为2017级本科生吴加隽,共同第一作者为2019级硕士生詹翊,通讯作者为王超研究员,第一单位为华中科技大学光学与电子信息学院及武汉光电国家研究中心。这也是我院第一次由本科生以第一作者身份在IEEE TCAS-I上发表学术论文。

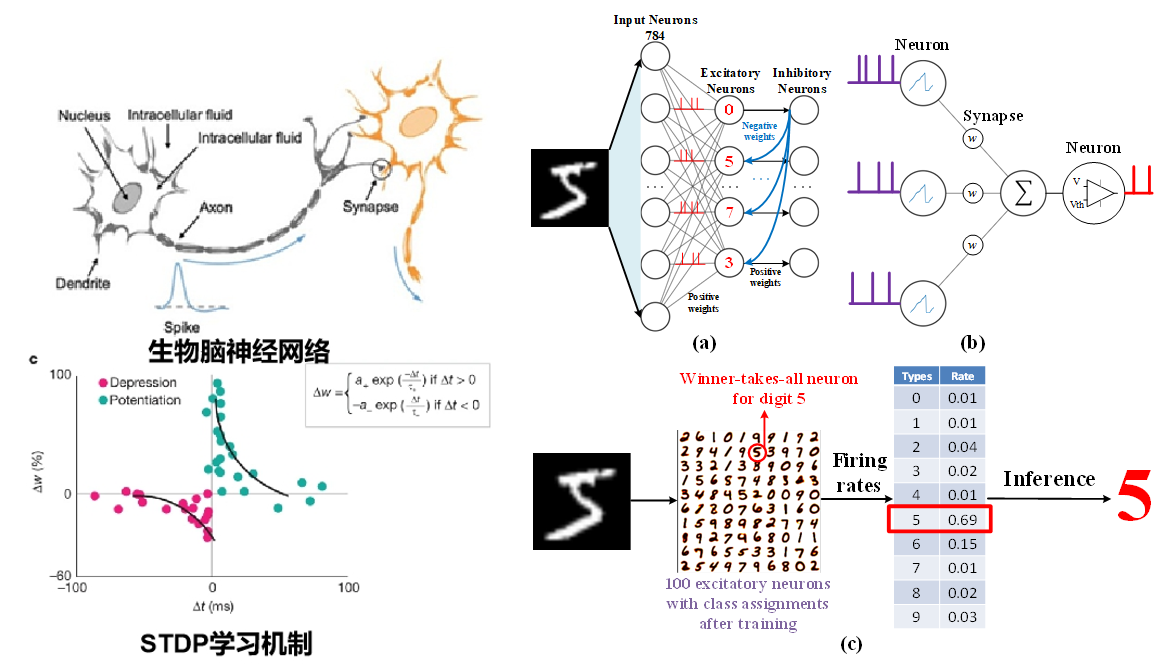

图1 受生物脑启发的类脑脉冲神经网络结构及其在图像识别的应用

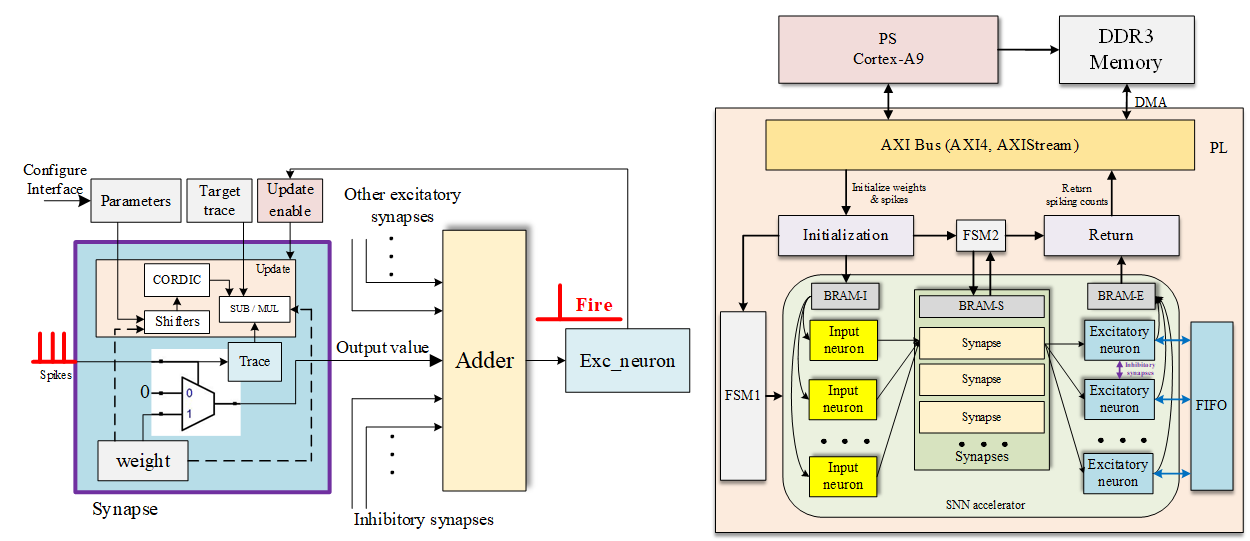

近年来,神经网络已经被用在许多模式识别、图像/语音分类和自然语言处理等任务中。然而,传统人工神经网络(ANN)的计算复杂度高、参数规模大,导致它很难在功耗受限制的场景发挥其高性能的优势。相比传统的人工神经网络,类脑脉冲神经网络拥有生物学习特性、事件驱动的局部学习机制,成为人工智能(AI)领域的研究热点。图1展示了这项工作选用的SNN模型,其局部学习算法符合脉冲时序依赖可塑性(Spiking-Timing-Dependent-Plasticity,简称STDP)机制(图1),具有生物可似性。同时,该工作用快速收敛CORDIC算法来完成基于STDP局部学习的运算,能够以更少的迭代次数来达到更优的学习性能。快速收敛CORDIC算法利用角度重编码(Angle-Recoding)机制,相比传统算法大大降低了所需的迭代次数。基于这种局部学习实现,该工作提出了时分复用架构,以处理图像识别任务。图2展示了该工作提出的基于快速收敛CORDIC的局部学习电路架构,以及FPGA系统验证架构。除此之外,论文对不同的STDP硬件实现方案(如基于不同的CORDIC算法和基于查找表等方法)做了全面的评估,从局部学习计算的误差开始分析,扩展到SNN应用级(标准数据集MNIST手写体图像识别)的精度评估。在评估结果中,基于快速收敛CORDIC算法的SNN能在几乎不损失识别精度的情况下,提升了45.3%的能量效率和提高了46.4%的学习速度;同时,获得了比其他方法更加出色的识别性能(图3所示,准确率高达95%),证明了该设计方案的高效性。

图2基于快速收敛CORDIC的局部学习突触电路架构,及FPGA验证系统架构

由于SNN的高能效性和类脑特性,SNN的硬件实现已经引起了集成电路与系统领域广泛的研究兴趣。在前人工作中,因为CORDIC算法可以被用于STDP学习机制中的局部计算,研究人员已经在小规模网络中对基于CORDIC的SNN进行了验证,且仿真了网络中神经元的动态特性。但学术界仍缺少基于CORDIC算法实现SNN的应用级评估,无法对SNN的实际应用(包括图像识别、语音识别等)提供指导。该研究工作为了填补这一学术领域的空缺,对基于不同的STDP硬件实现策略进行了全面的评估。在未来,我们会进一步寻找系统级的架构优化,且将SNN硬件实现扩展到实时性、能效要求更高的应用场景,例如将SNN用于更高分辨率、更多信息量的图像及生理信号实时处理中,并利用ASIC综合工具完成其硬件评估和集成电路芯片设计及流片。

图3所提基于快速收敛CORDIC的SNN方案(a)图像识别性能优于其他CORDIC方案(b)-(d)

该论文的第一作者吴加隽,为华中科技大学光电信息学院集成1703班本科生。除了这项工作以外,吴加隽作为集成专业本科生,还在低功耗与智能集成电路研究室参与了其他项目。在2020年11月,吴加隽参加了IEEE固态电路学会四大旗舰会议之一的IEEE亚洲固态电路会议(IEEE A-SSCC),在会议上对他所带领团队的工作——高能效、片上学习的类脑神经网络多核处理器进行口头报告与原型演示[2]。吴加隽自2019年春季加入王超研究员的低功耗与智能集成电路研究室以来,在自己感兴趣的领域不断探索,平衡课业压力与科研任务,始终以兴趣为导向,坚持每天做好研究计划,积极与课题组其他同学讨论交流。同时,他还通过王超老师的联系和推荐与新加坡科技与设计大学(SUTD)、南洋理工大学(NTU)、新加坡科技研究院(A*STAR)和澳门大学(UM)等境外一流学术机构进行了学习和交流,并积极参加了王超老师组织的多项IEEE CASS-EDS-SSCS武汉联合分会集成电路领域的学术活动,不仅开拓了学术视野和研究思路,而且获取了不少创新的灵感。通过这些努力,他收获了满意的成果,不仅以第一作者发表了集成电路与系统领域里的一篇顶级期刊论文和一篇高水平会议论文,而且获得了来自香港大学的攻读博士学位奖学金。吴加隽同学的这两项研究工作成果都获得了来自国家自然科学基金类脑神经网络芯片项目61974053的资助。

[1] J. Wu et.al, “Efficient Design of Spiking Neural Network with STDP Learning Based on Fast CORDIC,” in IEEE Trans. on Circuits and Systems-I Regular Papers (TCAS-I), 2021.

[2] J. Wu et.al, “An Energy-efficient Multi-core Restricted Boltzmann Machine Processor with On-chip Bio-plausible Learning and Reconfigurable Sparsity,” in Proc. of IEEE Asian Solid State Circuit Conference (A-SSCC 2020), 2020.